# Hardware-Aware Algorithms and Data Structures Gabriel Moruz

## PhD Dissertation

Department of Computer Science University of Aarhus Denmark

# Hardware-Aware Algorithms and Data Structures

A Dissertation Presented to the Faculty of Science of the University of Aarhus in Partial Fulfillment of the Requirements for the PhD Degree

> by Gabriel Moruz July 31, 2007

# Abstract

Various computer hardware components are affecting the running time of algorithms in different proportions, or may have severe implications on the accuracy of algorithms. In this dissertation we propose algorithms and data structures that are efficient and robust with respect to different hardware factors. The hardware factors affecting the running time that we consider include branch mispredictions occurring in the processor, memory transfers occurring between consecutive levels of the memory hierarchy in modern computers, as well as the high rate sequential access on modern hard-disks which is a major motivation for developing streaming algorithms. Regarding the factors affecting the accuracy of algorithms, we consider soft memory errors which determine corruptions in RAM memories.

Branch mispredictions incur significant performance losses for algorithms. First, we show that the running time of randomized Quicksort is adaptive, i.e. it depends on the presortedness of the input. We prove theoretically that the number of element swaps performed by Quicksort depends on the number *Inv* of inversions in the input and show experimentally that the number of element swaps is closely correlated to the number of branch mispredictions. We then give lower bound trade-offs between comparisons and branch mispredictions for sorting and adaptive sorting, and propose sorting and adaptive sorting algorithms matching these bounds. Finally, we show experimentally that for random queries perfectly balanced binary search trees can be outperformed by skewed binary search trees, i.e. trees for which at any given node there is a fixed ratio between the nodes in the left and right subtrees. This happens because the skewed binary search trees perform more comparisons, but fewer branch mispredictions, compared to perfectly binary search trees for random queries.

Memory transfers occurring between consecutive levels of the memory hierarchy in modern computers are modeled in the I/O model and cache oblivious model, and the complexity of algorithms is given by the number of memory transfers performed. We introduce I/O lower bounds for adaptive sorting algorithms and give two algorithms that are optimal and I/O optimal with respect to *Inv*.

In a streaming setting, algorithms are restricted to access data sequentially, while having at their disposal a working memory that can be accessed for free, but which is usually much smaller than the problem size. We give general reductions from parallel algorithms to streaming algorithms, and show that we can obtain optimal algorithms (up to poly-log factors) for several combinatorial problems, such as sorting, connected components, minimum spanning tree, biconnected components, or maximal independent set.

To analyze memory corruptions, we use the faulty-memory RAM model proposed by Finocchi and Italiano. In this model, any memory cell can get corrupted at any time during the execution of an algorithm, with no possibility of distinguishing between corrupted and uncorrupted cells. The number of corruptions is bounded by a parameter  $\delta$ , known to the algorithm, and O(1)corruption-free cells are provided. An algorithm is denoted resilient if it works correctly on the set of uncorrupted values. Our contributions include efficient resilient priority queues and resilient dictionaries.

# Acknowledgments

I am deeply grateful to my adviser Gerth Stølting Brodal, for the countless hours of discussions and for all the support he offered me throughout my Ph.D. studies. He has guided my first steps in research on algorithms and it has been a real pleasure to work with him.

Many thanks to the people forming the algorithms group at University of Aarhus. In particular, I would like to thank my co-author Rolf Fagerberg, now at University of Southern Denmark, and my co-authoring fellow Ph.D. students Allan Grønlund Jørgensen and Thomas Mølhave for all the work done together. Also, I would like to thank Lars Arge for establishing the great group that MADALGO is becoming.

I would like to thank Camil Demetrescu for agreeing to work with me during my abroad stay in Rome. Also, many thanks to the algorithms group at University of Rome "La Sapienza" for the helpful discussions. In particular, I would like to thank my co-authors Camil Demetrescu, Bruno Escoffier, and Andrea Ribichini for all the research conducted together during the period that I spent in Rome.

I am very thankful to all my colleagues and friends in Aarhus, in particular to Allan, Anders, Bjarke, Christopher, Claus, Daniel, Doina, Fitzi, Irit, Jan, Jesper, Jesus, Jooyong, Johan, Kevin, Kristoffer, Manuel, Marco, Martin, Michael, Mikkel, Mirka, Philipp, Roland, Rune, and Tord, for all the great moments spent together. Special thanks to Bartek for his help as a mentor, to Chris for co-winning two table football tournaments, to Saurabh and Kirill for their always cheerful attitude, to Henrik and Thomas for organizing the weekly soccer events, and to Gosia and Darek for gluing the group together.

I am very grateful to all the administrative and technical staff for ensuring that everything went smoothly, in particular (not exclusively) to: Mogens Nielsen, Uffe Engberg, Lene Kjeldsteen, Karen K. Møller, Ellen Lindstrøm, Hanne F. Jensen, Else Magård, and Michael Glad. Also, I would like to thank Danish National Research foundation for funding my studies at BRICS.

Last, but not least, I am grateful to my parents and my sister for their constant love and support over the years, and for being there for me all the time. Without them I could have never made it.

Gabriel Moruz, Århus, July 31, 2007.

# Contents

| A        | bstra | nct          |                        |  |  |  |   | $\mathbf{v}$   |  |  |

|----------|-------|--------------|------------------------|--|--|--|---|----------------|--|--|

| A        | ckno  | wledgn       | nents                  |  |  |  |   | vii            |  |  |

| 1        | Intr  | Introduction |                        |  |  |  |   |                |  |  |

|          | 1.1   | Hardw        | vare                   |  |  |  |   | 2              |  |  |

|          | 1.2   | Model        | ling hardware          |  |  |  |   | 4              |  |  |

|          | 1.3   | Algori       | thmic problems studied |  |  |  |   | 6              |  |  |

|          | 1.4   | Contri       | butions                |  |  |  |   | $\overline{7}$ |  |  |

|          | 1.5   | Outlin       | le                     |  |  |  | • | 10             |  |  |

| <b>2</b> | Har   | dware        |                        |  |  |  |   | 11             |  |  |

|          | 2.1   | Proces       | ssor                   |  |  |  |   | 11             |  |  |

|          |       | 2.1.1        | Execution engine       |  |  |  |   | 13             |  |  |

|          |       | 2.1.2        | Branch mispredictions  |  |  |  |   | 13             |  |  |

|          | 2.2   | Memo         | ry hierarchy           |  |  |  |   | 16             |  |  |

|          |       | 2.2.1        | Registers and caches   |  |  |  |   | 18             |  |  |

|          |       | 2.2.2        | Main memory            |  |  |  |   | 20             |  |  |

|          |       | 2.2.3        | Hard-disk              |  |  |  |   | 20             |  |  |

|          | 2.3   | Memo         | ry corruptions         |  |  |  | • | 20             |  |  |

| 3        | Mo    | deling       | Hardware               |  |  |  |   | 23             |  |  |

|          | 3.1   | Tradit       | ional models           |  |  |  |   | 23             |  |  |

|          |       | 3.1.1        | RAM model              |  |  |  |   | 24             |  |  |

|          |       | 3.1.2        | Comparison model       |  |  |  |   | 24             |  |  |

|          | 3.2   | Branc        | h mispredictions       |  |  |  |   | 24             |  |  |

|          | 3.3   | Extern       | nal memory models      |  |  |  |   | 25             |  |  |

|          |       | 3.3.1        | I/O model              |  |  |  |   | 26             |  |  |

|          |       | 3.3.2        | Cache-oblivious model  |  |  |  |   | 26             |  |  |

|          | 3.4   | Stream       | ning models            |  |  |  |   | 27             |  |  |

|          |       | 3.4.1        | Classical streaming    |  |  |  |   | 28             |  |  |

|          |       | 3.4.2        | W-Stream               |  |  |  |   | 28             |  |  |

|          |       | 3.4.3        | StrSort                |  |  |  |   | 28             |  |  |

|          | 3.5   | Faulty       | -memory RAM            |  |  |  |   | 28             |  |  |

| 4        | Cac  | he-Aware and Cache-Oblivious Adaptive Sorting                                                              | 31 |

|----------|------|------------------------------------------------------------------------------------------------------------|----|

|          | 4.1  | $\rm I/O$ lower bounds                                                                                     | 31 |

|          | 4.2  | GroupSort                                                                                                  |    |

|          | 4.3  | Cache-aware GenericSort                                                                                    | 35 |

|          | 4.4  | Cache-oblivious GenericSort                                                                                | 36 |

|          | 4.5  | GreedySort                                                                                                 | 38 |

| <b>5</b> | On   | the Adaptiveness of Quicksort                                                                              | 41 |

|          | 5.1  | Expected number of swaps by randomized                                                                     |    |

|          |      | Quicksort                                                                                                  | 41 |

|          | 5.2  | Experimental setup                                                                                         | 46 |

|          | 5.3  | Experimental results                                                                                       | 47 |

|          |      | 5.3.1 Quicksort. $\ldots$ | 47 |

|          |      | 5.3.2 Mergesort. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                   | 48 |

|          | 5.4  | Conclusions and related work                                                                               | 49 |

| 6        | Trac | ding Branch Mispredictions for Comparisons when Sorting                                                    | 57 |

|          | 6.1  | Lower bounds for sorting                                                                                   | 57 |

|          | 6.2  | An optimal sorting algorithm                                                                               | 59 |

|          | 6.3  | Optimal adaptive sorting                                                                                   | 60 |

| 7        | Ske  | wed Binary Search Trees                                                                                    | 63 |

|          | 7.1  | Skewed binary search trees                                                                                 | 63 |

|          | 7.2  | Hardware discussion                                                                                        | 64 |

|          | 7.3  | Branch mispredictions                                                                                      | 65 |

|          | 7.4  | Memory layouts                                                                                             | 66 |

|          | 7.5  | Experimental setup                                                                                         | 68 |

|          | 7.6  | Experimental results                                                                                       | 68 |

| 8        | Ada  | opting parallel algorithms to the W-Stream model                                                           | 73 |

|          | 8.1  | Simulating parallel algorithms in W-Stream                                                                 | 73 |

|          | 8.2  | Sorting                                                                                                    | 75 |

|          | 8.3  | Graph problems                                                                                             | 76 |

|          |      | 8.3.1 Connected components (CC)                                                                            | 76 |

|          |      | 8.3.2 Minimum spanning tree (MST)                                                                          | 77 |

|          |      | 8.3.3 Biconnected components (BCC)                                                                         | 78 |

|          |      | 8.3.4 Maximal independent set (MIS)                                                                        | 80 |

|          | 8.4  | Limits of the RPRAM approach                                                                               | 81 |

| 9        | Res  | ilient Priority Queues                                                                                     | 83 |

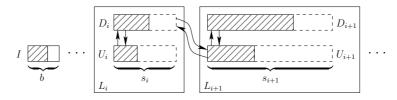

|          | 9.1  | Preliminaries                                                                                              | 83 |

|          | 9.2  | Fault tolerant priority queue                                                                              | 83 |

|          |      | 9.2.1 Structure                                                                                            | 84 |

|          |      | 9.2.2 Push and pull primitives                                                                             | 85 |

|          |      | 9.2.3 Insert and deletemin                                                                                 | 86 |

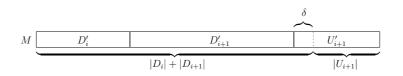

|          | 9.3  | Analysis                                                                                                   | 87 |

|          |      | 9.3.1 Correctness                                                                                          | 87 |

| 9.3.2 Complexity $\ldots$                                                              |  |   | 88  |  |  |  |

|----------------------------------------------------------------------------------------|--|---|-----|--|--|--|

| 9.4 Lower bound                                                                        |  | • | 90  |  |  |  |

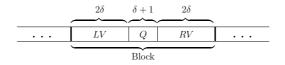

| 10 Optimal Resilient Dynamic Dictionaries                                              |  |   |     |  |  |  |

| 10.1 Optimal randomized static dictionary                                              |  |   | 91  |  |  |  |

| 10.2 Optimal static dictionary                                                         |  |   | 93  |  |  |  |

| 10.3 Dynamic dictionary $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |  |   | 97  |  |  |  |

| Bibliography                                                                           |  | 1 | .01 |  |  |  |

# List of Figures

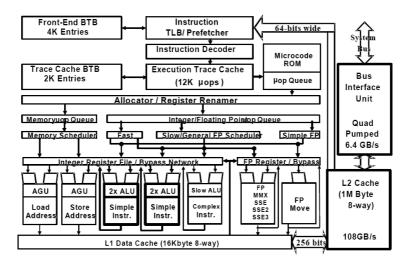

| 2.1  | The architectures for Intel Pentium 4 [17]                                     | 12 |

|------|--------------------------------------------------------------------------------|----|

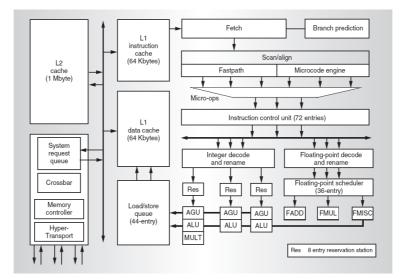

| 2.2  | The architectures for AMD Opteron [73].                                        | 12 |

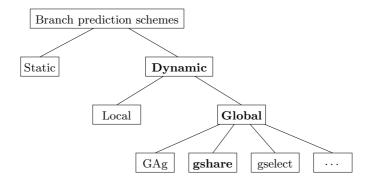

| 2.3  | A classification of the branch prediction schemes                              | 14 |

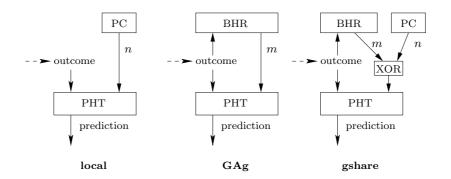

| 2.4  | Popular branch prediction schemes                                              | 15 |

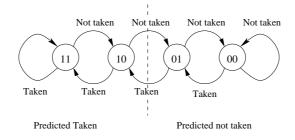

| 2.5  | Two-bit saturating counter.                                                    | 15 |

| 2.6  | Simple example demonstrating the effect of branch mispredic-                   |    |

|      | tions over the running time                                                    | 16 |

| 2.7  | The running time of the code in Figure 2.6.                                    | 16 |

| 2.8  | Simple example demonstrating the effect that memory transfers                  |    |

|      | have over the running time                                                     | 17 |

| 2.9  | Running time of the highlighted code in Figure 2.8                             | 18 |

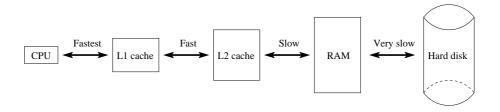

| 2.10 | Typical memory hierarchy in a modern computer                                  | 18 |

| 0.1  |                                                                                | 20 |

| 3.1  | The I/O model                                                                  | 26 |

| 3.2  | Typical memory hierarchy in a modern computer                                  | 27 |

| 4.1  | Lower bounds on the number of I/Os and the number of com-                      |    |

|      | parisons                                                                       | 32 |

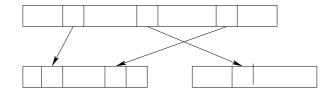

| 4.2  | Linear time reduction to non-adaptive sorting.                                 | 34 |

|      |                                                                                |    |

| 5.1  | C code for randomized Quicksort                                                | 42 |

| 5.2  | Example of succesive partitions for randomized Quicksort                       | 42 |

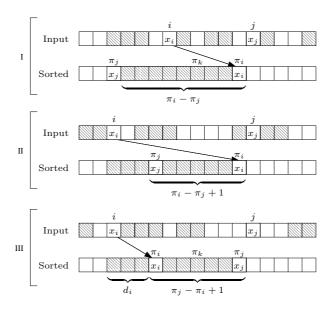

| 5.3  | The three different cases of Lemma 5.2.                                        | 43 |

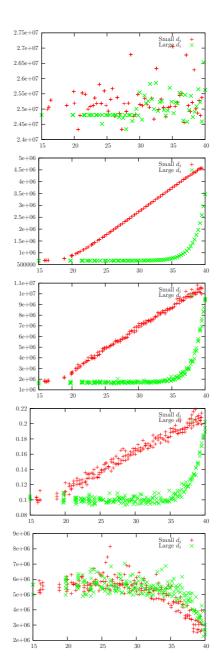

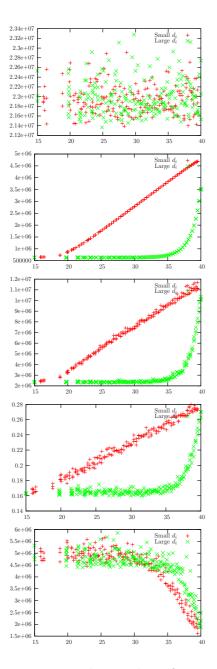

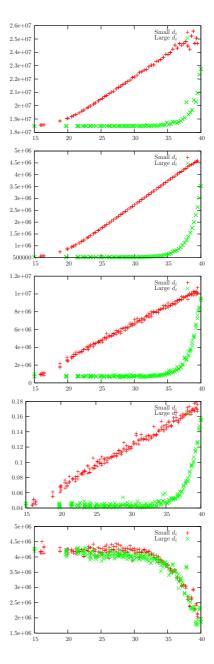

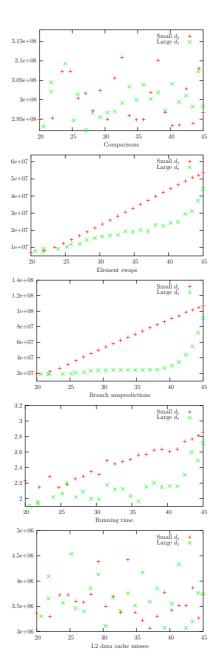

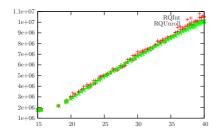

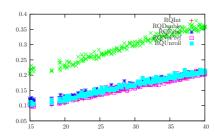

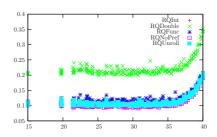

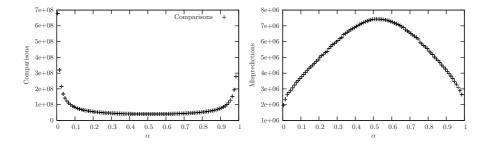

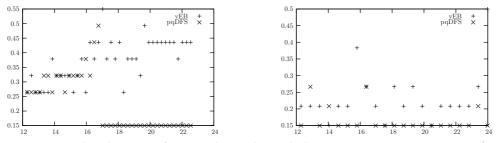

| 5.4  | Experimental results for randomized Quicksort on Athlon                        | 50 |

| 5.5  | Experimental results for randomized Quicksort on P4                            | 50 |

| 5.6  | Experimental results for randomized median-of-three Quicksort                  |    |

|      | on P4                                                                          | 51 |

| 5.7  | Experimental results for deterministic Quicksort on P4                         | 51 |

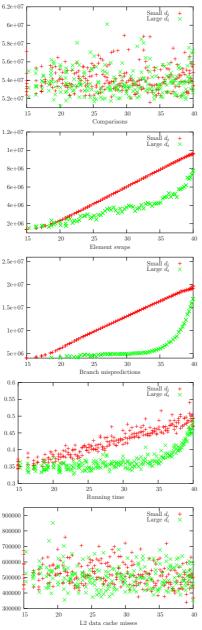

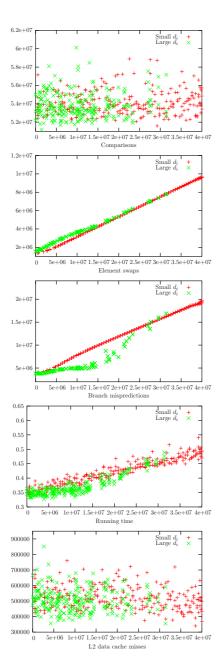

| 5.8  | Experimental results for randomized Quicksort with small inputs.               | 52 |

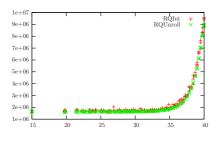

| 5.9  | Experimental results for randomized Quicksort with large inputs.               | 52 |

| 5.10 | Experimental results with $\sum_{i=1}^{n} \log(d_i + 1)$ on the <i>x</i> -axis | 53 |

| 5.11 | Experimental results for Heapsort.                                             | 53 |

| 5.12 | Experimental results for Mergesort                                             | 54 |

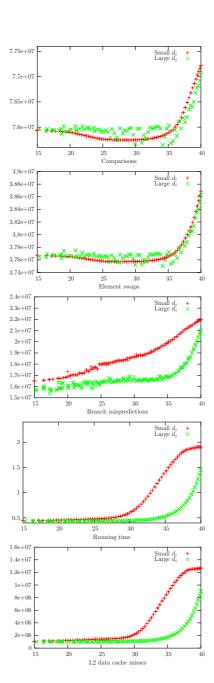

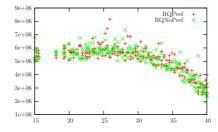

| 5.13 | The number of branch mispredictions for two implementations                    |    |

|      | of randomized Quicksort for small $d_i$ 's                                     | 54 |

| 5.14 | The number of branch mispredictions for two implementations                    |    |

|      | of randomized Quicksort for large $d_i$ 's                                     | 54 |

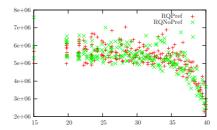

|                   | The number of L1 data cache misses for randomized Quicksort<br>for small $d_i$ 's with the hardware prefetcher turned on and off<br>The number of L1 data cache misses for randomized Quicksort | 55       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.17              | for large $d_i$ 's with the hardware prefetcher turned on and off<br>Running time for various implementations of randomized Quick-                                                              | 55       |

| 5.18              | sort for small $d_i$ 's                                                                                                                                                                         | 55<br>55 |

| 6.1<br>6.2        | Lower bounds on the number of branch mispredictions for deter-<br>ministic comparison based adaptive sorting algorithms<br>Greedy division protocol                                             | 59<br>61 |

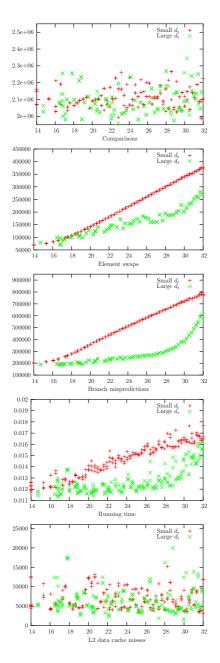

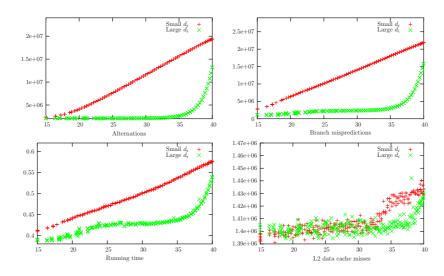

| 7.1<br>7.2<br>7.3 | Bound on the expected cost for a random search An iterative C source code for searching                                                                                                         | 64<br>69 |

| 7.4               | dictions performed by a skewed search tree                                                                                                                                                      | 69       |

| $7.5 \\ 7.6$      | formed by a skewed search tree for the non-blocked layouts The best running times for $k$ -level grouping and pqDFS The running time and the number of L1 data cache misses per-                | 72<br>72 |

| 7.7               | formed by a skewed search tree for the blocked layouts The skewness factors that achieved the minimum running times for different tree sizes                                                    | 72<br>72 |

| 9.1               | The structure of the resilient priority queue                                                                                                                                                   | 84       |

| 9.2               | The distribution of $M$ into buffers                                                                                                                                                            | 87       |

| 10.1              | $LV$ and $RV$ , contain $2\delta$ elements each, and the query segment                                                                                                                          |          |

| 10.2              | $Q$ contains $\delta + 1$ elements                                                                                                                                                              | 93       |

| 10.3              | element is corrupted                                                                                                                                                                            | 94       |

| 10.4              | failure. The emphasized elements are corrupted                                                                                                                                                  | 95<br>97 |

# Chapter 1

## Introduction

A journey of a thousand miles begins with a single step. — Lao-tzu

Since the early days of computer science, the design and analysis of algorithms emerged as a fundamental research area. Having in mind that every program running in a computer is based on an algorithm, developing fast algorithms is a key factor towards developing fast software. In this dissertation, we show that a major point in developing fast algorithms is taking advantage of the characteristics of the underlying hardware. We focus on hardware factors that have a great influence over the running time or the reliability of algorithms. Among the factors affecting the running time we focus on branch mispredictions, block transfers between the consecutive levels of the memory hierarchy, and the high sequential access rate on modern hard-disks which motivates streaming. We consider also memory corruptions caused by soft memory errors in RAM memories and consequently design algorithms and data structures aware of possibly corrupted data.

Typically, the performance of algorithms is quantified by measures like instructions performed by the CPU or memory accesses. From this perspective, efficient algorithms for an endless series of problems have been introduced during the past decades. However, a number of assumptions with respect to the actual behavior of the hardware have been made. Since these assumptions do not always hold, this creates a potential gap between the theoretical algorithm design and analysis on one hand and the actual behavior of algorithms in practice on the other hand. For instance, a typical assumption is that all the instructions have the same execution time. Should this be the case for most instructions, in the case of conditional branches it is not always true, since they may take as much as 30 CPU cycles to execute [103]. Another standard assumption is that all memory accesses take the same time. This is certainly not the case in practice, since, due to memory hierarchies found in most computers, accessing data stored in the CPU registers is about 10,000,000 times faster than accessing data stored on disk [61]. A problem getting more and more important to address, motivated by the memory design technologies and the seeming unending increase in storage requirements, is that the cells in RAM memories may get corrupted in practice by e.g. alpha particles, radiation or cosmic rays, and

therefore assuming at all times a reliable memory may have dire consequences on the output of algorithms.

The remainder of this chapter is structured as follows. We briefly describe modern hardware in Section 1.1, and then we show in Section 1.2 why traditional models used for analyzing algorithms are not always accurate. We then introduce the algorithmic problems we consider in Section 1.3, and a summary of the contributions of the present dissertation in Section 1.4. This chapter concludes with an outline of the rest of the dissertation in Section 1.5.

#### 1.1 Hardware

In this section we briefly introduce the hardware architecture of modern computers, emphasizing the factors that have a strong effect on the running time of algorithms in practice. Also, we show that memory corruptions that occur in the RAM memories can have dramatic effects on the output of algorithms. A thorough discussion concerning the hardware is given in Chapter 2.

Nowadays computers are cutting-edge machineries, consisting of highly complex components, and hardware technologies evolve at an incredibly fast pace. For instance, based on an empirical observation, Moore's law [119] states that the number of transistors contained on an integrated circuit doubles every 24 months. Following this law, nowadays CPU's may contain as much as 125 millions transistors, in the case of Intel Pentium 4 Extreme [61]. Furthermore, similar laws state that storage capacity for RAM memories increases at the same rate as processing power, and that the rate of progression in hard-disk storage over the past decades has sped up more than once.

The running time of algorithms in practice is the result of interaction of a wide range of factors, occurring at all hardware levels. In the following we give brief descriptions of the hardware factors discussed in the present dissertation.

**Instructions count.** The classical way of determining the running time of algorithms was counting the number of instructions performed by the CPU. Even though there are several more factors affecting the running time, instruction count is still a good indicator for the performance of algorithms. However, due to improvements in CPU design, such as increasing the frequencies and the ability to execute multiple instructions per cycle, modern processors are able to execute more instructions in a time unit and consequently the number of instructions performed is diminishing its influence over the running time.

**Branch mispredictions.** To increase the clock speed, modern CPUs include instruction pipelines in their architecture, where the instructions are prefetched before being executed. When a conditional branch enters the pipeline, its outcome is not known prior to its execution and thus its direction must be predicted to ensure the prefetching of the following instructions. If the branch is incorrectly predicted, the whole pipeline must be flushed, since the instructions in the pipeline correspond to a wrong execution path. This obviously leads to a performance loss, which increases proportionally with the length of the pipeline.

#### 1.1. Hardware

In such a case, we say that a *branch misprediction* occurs. Since the pipelines are getting longer and longer (e.g. as much as 18 instructions for Pentium P4 and 31 for Intel Prescott), branch mispredictions are having an increasing influence over the running time of algorithms in practice.

To predict the outcome of conditional branches, modern CPUs employ *branch predictors*, which implement *branch prediction schemes*. There are two major categories of branch prediction schemes, static and dynamic. In a static prediction scheme, a conditional branch is predicted the same way every time, and its direction is set based on simple heuristics, e.g. predict forward branches taken and backward branches not taken. Dynamic branch prediction schemes are more complex and use the execution history to predict the direction of a branch. The increased complexity of dynamic branch predictors proves to be very useful in increasing the amount of succesfully predicted branches, achieving a rate of success of about 90%.

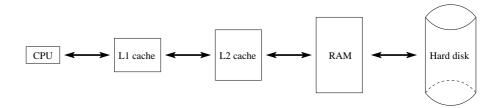

I/O transfers. Modern computers have several memory levels, each level having smaller size and access time than the next one. Typically, a desktop computer contains CPU registers, L1, L2, and L3 caches, main memory and hard-disk. The access time increases from one or even half a cycle for registers and level 1 cache to around 10, 100 and 10,000,000 cycles for level 2 cache, main memory and disk, respectively [61]. Therefore, the I/O transfers between memory and disk often become a bottleneck with respect to the running time of a given algorithm, and minimizing the number of I/O transfers is a necessary step towards achieving fast running times.

**Streaming.** Data stream processing has gained increasing popularity in the last few years as an effective paradigm for processing massive data sets. Huge data streams arise in several modern applications, including database systems, IP traffic analysis, sensor networks, and transaction logs [55,56,110]. Streaming is an effective paradigm also in scenarios where the input data is not necessarily represented as a data stream. Due to high sequential access rates of modern disks, streaming algorithms can be effectively deployed for processing massive files on secondary storage [62].

Memory corruptions. Memory devices continually become smaller, work at higher frequencies and lower voltages, and in general have increased circuit complexity [32]. Unfortunately, these improvements come at the cost of reliability [113, 114]. A number of factors, such as alpha particles, infrared radiation, and cosmic rays, can cause *soft memory errors* where a bit flips and as a consequence the value stored in the corresponding memory cell is corrupted. An unreliable memory can cause a variety of problems in most software, ranging from harmless to the very serious, such as breaking cryptographic protocols [18, 120], taking control of a Java Virtual Machine [57] or breaking smart-cards and other security processors [5, 6, 108]. Also, the output of algorithms that are unaware of possibly corrupted memories may be severely affected. A typical example concerns merging two sorted sequences, where a single corrupted memory cell may induce as much as  $\Theta(n^2)$  inversions in the output sequence [51].

## 1.2 Modelling hardware

The running time of algorithms is usually analyzed by counting the instructions performed by the CPU on an abstract model of computation, e.g. the RAM model. However, we argued that in practice some other hardware factors, in addition to CPU instructions, can have a non-negligible effect over the running time of an algorithm. In this section we briefly introduce the models that handle the different hardware factors.

**Traditional models.** Traditionally, the time complexity of algorithms is computed by counting the number of instructions performed by the CPU. Below we introduce two of the most popular models of computation, the RAM model and the comparison model.

- *RAM model.* The RAM (Random Access Machine) model is an abstraction of a real-world computer. It consists of a CPU and a memory of unlimited size, where CPU instructions and memory accesses take the same amount of time. The complexity of an algorithm is given by the number of instructions and memory accesses performed.

- *Comparison model.* In this model, the complexity of an algorithm is given by the number of comparisons performed. Though it does not include all the instructions performed by the CPU, the comparison model is suitable when dealing with problems where comparisons are the key instructions, e.g. sorting and searching.

**Branch mispredictions.** When analyzing the branch misprediction complexity of an algorithm, we will use a static prediction scheme. In such a scheme, every branch is predicted the same direction at all times. Basically, we assign for each branch *a priori* a direction in which it will be predicted during the execution of the algorithm. A major drawback in using static prediction schemes to analyze the branch misprediction complexity of algorithms is that they are less accurate than the dynamic prediction schemes in practice. However, static prediction schemes are simple to analyze and are suited for hard problems, such as sorting and searching, where the output of a comparison is very hard to predict.

**I/O transfers.** Several models have been proposed to capture the effect of memory hierarchies. We describe two of the most successful, the I/O model and the cache-oblivious model.

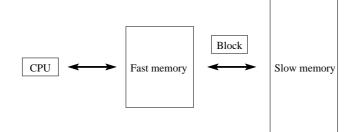

I/O model. The I/O model was introduced by Aggarwal and Vitter [1]. It is a model closer to real world hardware and models a simple two-level memory hierarchy consisting of a fast memory of size M and a slow infinite memory. The data transfers between the slow and fast memory are performed in *blocks* of size B of consecutive data. In this model the algorithm has full control of the memory management, including location of the data and the replacement policy. The performance of an algorithm is given by its I/O complexity, which is obtained by counting the number of transfers it performs between the slow and the fast memories.

Cache-oblivious model. A drawback of the I/O model is the assumption that the size M of the fast memory and the block size B are known, which does not always hold in practice. Moreover, as the modern computers have multiple memory levels with different sizes and block sizes, different parameters are required at the different memory levels. Frigo et al. [52] proposed the *cache-oblivious model*, which is similar to the I/O model, but assumes no knowledge about M and B. In short, a cache-oblivious algorithm is an algorithm described in the RAM model, but analyzed in the I/O model with an analysis valid for any values of M and B. The power of this model is that if a cache-oblivious algorithm performs well on a two-level memory hierarchy with arbitrary parameters, it performs well between all the consecutive levels of a multi-level memory hierarchy. Since the algorithm is oblivious of the memory it operates on, a standard assumption of this model is an optimal replacement strategy for the underlying memory levels. Also, most algorithms require a tall cache assumption, i.e.  $M = \Omega(B^{1+\varepsilon})$ .

**Streaming.** In the recent years, due to increased popularity of data stream processing, several streaming models have been proposed. In such models, the input data is accessed sequentially, using a small amount of working memory, which is usually much smaller than the input size [13,62,87,88]. Typical parameters in streaming models include the number p of passes over the input stream and the number s of bits contained by the working memory. In the following we list some of the streaming models.

- *Classical streaming.* In classical streaming, the input stream is read-only, and we are interested in algorithms that require one (or few) passes for solving a given problem. Given the little amount of resources that a streaming algorithm has, typical results obtained in this model are approximations of an exact solution.

- *W-Stream.* The W-Stream model was introduced by Demetrescu et al. [37]. In this model, at each pass we operate with an input stream and an output stream. The streams are pipelined in such a way that the output stream produced at pass i is given as input stream at pass i + 1.

- StrSort. StrSort model is just W-Stream augmented with a sorting primitive that can be used at each pass to reorder the output stream at no cost, and is motivated by the fact that sorting is a well-studied problem in the context of massive inputs. Sorting provides a significant amount of computational power, making it possible to solve several graph problems using poly-log passes and working space [2].

Memory corruptions. In practice, cells in RAM memories may get corrupted as a result of soft memory errors. Since most algorithms assume a reliable memory, they are not designed to handle memory corruptions and their output may be severely affected. A classical example concerns merging two sorted sequences, where a single memory corruption may induce as many as  $\Theta(n^2)$  inversions [51]. To design algorithms that are aware of memory corruptions, we use the *faulty-memory random access machine*, introduced by Finocchi and Italiano [51]. A faulty-memory RAM is a random access machine where the content of memory cells can get corrupted at any time and at any *location*. Corrupted cells cannot be distinguished from uncorrupted cells. The model is parametrized by an upper bound  $\delta$  on the number of corruptions occurring during the lifetime of an algorithm. It is assumed that O(1) reliable memory cells are provided, a reasonable assumption since CPU registers are considered reliable. Also, copying an element is considered an atomic operation, i.e. the elements are not corrupted while being copied. An algorithm is resilient if it is able to achieve a correct output at least for the uncorrupted values. This is the best one can hope for, since the output can get corrupted just after the algorithm finishes its execution. For instance a resilient sorting algorithm guarantees that there are no inversions between the uncorrupted elements in the output sequence.

## **1.3** Algorithmic problems studied

In this section we give an overview of the problems studied throughout the rest of the dissertation. We are interested in developing algorithms and data structures that are aware of the various hardware factors affecting the running time. We develop algorithms for fundamental problems, such as sorting, adaptive sorting, and basic algorithms for undirected graphs (e.g. connected components, minimum spanning tree, biconnected components, maximal independent set). Also, we study fundamental data structures, such as priority queues and static and dynamic dictionaries.

**Sorting and adaptive sorting** Given a sequence of elements from a totally ordered universe, sorting means producing a sequence containing all the elements in non-decreasing order.

A well known fact concerning sorting is that optimal sorting algorithms perform  $\Theta(n \log n)$  comparisons [34, Section 9.1]. However, in practice there are many cases where the input sequences are already nearly sorted, i.e. have low disorder according to some measure [74,85]. In such cases one can hope for a sorting algorithm to be faster.

In order to quantify the disorder of input sequences, several measures of presortedness have been proposed, e.g. see [43,74,82]. One of the most commonly considered measures is Inv, the number of inversions in the input, defined by  $Inv(X) = |\{(i, j) \mid i < j \land x_i > x_j\}|$  for a sequence  $X = (x_1, \ldots, x_N)$ . Other examples of measures include: Runs, the number of boundaries between ascending subsequences; Max, the largest difference between the ranks of an element in the input and the sorted sequence; *Dis*, the largest distance determined by an inversion. A sorting algorithm is denoted *adaptive* if the time complexity is a function dependent on the size as well as the presortedness of the input sequence [85]. For an overview concerning adaptive sorting, see e.g. the survey by Estivill-Castro and Wood [45]. More recent works include [39–41, 90, 93].

Manilla [82] introduced the concept of optimality of an adaptive sorting algorithm in the comparison model. An adaptive sorting algorithm S is optimal with respect to some measure of presortedness  $\mathcal{D}$ , if for some constant c > 0and for all inputs X, the time complexity  $T_A(X)$  satisfies

$T_A(X) \leq c \cdot \max(N, \log |\text{below}(X, \mathcal{D})|)$ ,

where below  $(X, \mathcal{D})$  is the number of permutations of the input sequence Y for which  $\mathcal{D}(Y) \leq \mathcal{D}(X)$  and  $\log x$  denotes  $\log_2 x$ . By the usual information theoretic lower bound, this is asymptotically the best possible. In particular, an adaptive sorting algorithm that is optimal with respect to the measure Invperforms  $\Theta(N(1 + \log(1 + Inv/N)))$  comparisons [58].

**Priority queues.** A priority queue is a data structure that contains a set of elements drawn from a totally ordered universe, supporting two operations, INSERT and DELETE-MIN. The INSERT operation inserts an element, while the DELETE-MIN operation returns and removes the element having the smallest key from the data structure. In addition, priority queues may support various operations such as decrease-key, deletions, melding, in addition to the two standard ones,

Static and dynamic dictionaries. A dictionary is a data structure that contains a totally ordered set of elements. Given a search key x, a static dictionary returns a boolean value stating whether x is contained in the data structure or not. A dynamic dictionary supports also updates, i.e. insertions and deletions, in addition to searches.

**Graph algorithms.** Consider an undirected graph G = (V, E). A connected component of G is a maximal set of vertices  $V' \subseteq V$  such that there exists a path between any pair of vertices in V'. A biconnected component of a graph G is a maximal subset of edges E' such that in the subgraph induced by E' there are two node-disjoint paths between any pair of vertices.

Consider a connected undirected graph G = (V, E) having weighted edges, i.e. every edge (u, v) is assigned a cost w(u, v). A minimum spanning tree T of G is a tree containing all the vertices in V and having minimal cost, i.e.  $\sum_{(u,v)\in T} w(u, v)$  is minimal.

## 1.4 Contributions

In this section we list the main contributions of the present dissertation. We give detailed description of our results in Chapters 4-10, which present the work

published in  $[24, 28-31, 36, 70]^1$ .

Cache-aware and cache-oblivious adaptive sorting (Chapter 4, [28]). We recall that sorting algorithms are denoted adaptive if their running times depend not only on the input size, but also on some measure of presortedness quantifying how close to being sorted the input is. A popular measure of presortedness is the number Inv of inversions in the input sequence. In [28] we first provide lower bounds on the number of I/O transfers for various measures of presortedness. We then introduce two adaptive sorting algorithms which are optimal with respect to Inv. From both algorithms we derive adaptive sorting algorithms that are optimal with respect to Inv in both the I/O model and the cache-oblivious model.

Quicksort is adaptive (Chapter 5, [29]). Quicksort was introduced by Hoare [64,65]. It is a simple in-place, randomized sorting algorithm that became very popular over the last decades. A text-book result states that Quicksort is optimal (expected case), i.e. it performs expected  $\Theta(n \log n)$  comparisons [34]. A known fact is that Quicksort is not adaptive, since it performs expected  $O(n \log n)$  comparisons even when the input sequence is sorted. In [29] we demonstrate empirically that the running time of Quicksort is adaptive with respect to the number of inversions Inv in the input. Differences in running times close to a factor of two are observed between instances with low and high Inv values. We prove that Quicksort performs expected  $O(n(1 + \log(1 + Inv/n)))$  element swaps, where Inv denotes the number of inversions in the input sequence. This result provides a theoretical explanation for the observed behavior in practice, and gives new insights on the behavior of the Quicksort algorithm. We also give some experimental results on the adaptive behavior of Heapsort and Mergesort.

Optimal tradeoffs between comparisons and branch mispredictions for sorting algorithms (Chapter 6, [30]). In [30] we consider tradeoffs between the number of branch mispredictions and the number of comparisons for sorting algorithms in the comparison model, where each comparison is followed by a branch. We prove that a sorting algorithm using  $O(dn \log n)$  comparisons performs  $\Omega(n \log_d n)$  branch mispredictions. We show that Multiway Merge-Sort achieves this tradeoff by adopting a multiway merger with a low number of branch mispredictions. For adaptive sorting algorithms we similarly obtain that an algorithm performing  $O(dn(1 + \log(1 + Inv/n)))$  comparisons must perform  $\Omega(n \log_d(1 + Inv/n))$  branch mispredictions, where Inv is the number of

<sup>&</sup>lt;sup>1</sup>The paper **Optimal Resilient Dynamic Dictionaries** by Gerth S. Brodal, Rolf Fagerberg, Irene Finocchi, Fabrizio Grandoni, Giuseppe F. Italiano, Allan G. Jørgensen, Gabriel Moruz, and Thomas Mølhave [24], has been accepted for publication as a merged paper. The original contributions were **Resilient Search Trees: Randomization and Prejudice**, by Irene Finocchi, Fabrizio Grandoni, and Giuseppe F. Italiano, and **Optimal Resilient Dynamic Dictionaries**, by Gerth S. Brodal, Rolf Fagerberg, Allan G. Jørgensen, Gabriel Moruz, and Thomas Mølhave. The contributions of the latter will appear as a technical report in [27].

inversions in the input. This tradeoff can be achieved by the algorithm GenericSort by Estivill-Castro and Wood by adopting a multiway division protocol and a multiway merging algorithm with a low number of branch mispredictions.

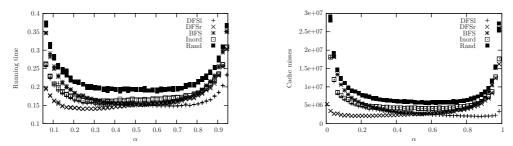

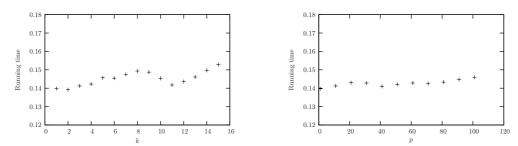

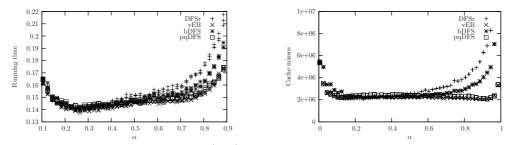

Skewed binary search trees (Chapter 7, [31]). It is well known that binary search trees achieve the best performance for a random search when they are perfectly balanced. Should this statement be true for the number of comparisons, which is indeed minimal when the trees are perfectly balanced, it does not hold for the running time. In [31], we study static skewed binary search trees, where for each node the ratio between the number of nodes in the left subtree and the size of the tree is a fixed constant. We show experimentally that skewed binary search trees can outperform perfectly balanced search trees by as much as 15% in running time. These improvements are due to the fact that during a search branching to the left or right at a node does not necessarily have the same cost, because of branch mispredictions. Basically, the more skewed the search tree is, the more comparisons and fewer branch mispredictions it performs. Also, previous work has shown that a dominating factor over the running time for a search is the number of cache faults performed, and that an appropriate memory layout of a binary search tree can reduce the number of cache faults by several hundred percent. We give an experimental study of various memory layouts of static skewed binary search trees, where each element in the tree is searched for with a uniform probability.

Parallel algorithms are good for streaming (Chapter 8, [36]). We show in [36] how to simulate parallel algorithms to obtain efficient algorithms in the W-Stream model. Motivated by the fact that simulating classical PRAM algorithms does not always help in achieving good results in the W-Stream model, we introduce a new model of computation denoted RPRAM (Relaxed PRAM). Basically a RPRAM is a classical PRAM where a processor is no longer constrained to access O(1) memory cells in a parallel round, but can access as much as all the cells in the memory. By simulating RPRAM algorithms in the W-Stream model we are able to achieve optimal W-Stream algorithms (up to poly-log factors) for several classical combinatorial problems, such as sorting, connected components, minimum spanning tree, biconnected components, and maximal independet set.

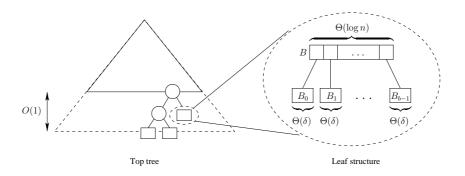

Resilient priority queues (Chapter 9, [70]). We recall that in the faultymemory RAM memory cells can get corrupted at any time and at any place during the execution of an algorithm, and the number of corruptions is upper bounded by a parameter  $\delta$ . An algorithm or data structure is denoted resilient if it works correctly on the set of uncorrupted values. In particular, for priority queues, the DELETEMIN operation returns the minimum uncorrupted value or some corrupted value. In [70] we introduce a resilient priority queue which uses O(n) space to store n elements, and supports both insert and deletemin operations in  $O(\log n + \delta)$  time amortized. Our priority queue matches the performance of classical optimal priority queues in the RAM model when the number of corruptions tolerated is  $O(\log n)$ . We prove matching worst case lower bounds for resilient priority queues storing only structural information in the uncorruptible registers between operations.

**Optimal resilient dictionaries (Chapter 10, [24]).** We introduce in [24] two optimal resilient static dictionaries, a randomized one and a deterministic one. The randomized dictionary supports searches in  $O(\log n + \delta)$  expected time using  $O(\log \delta)$  random bits in the worst case under the assumption of an oblivious adversary. The deterministic dictionary supports searches in  $O(\log n + \delta)$  time in the worst case. We introduce a dynamic resilient dictionary supporting searches in  $O(\log n + \delta)$  time in the worst case, which is optimal, and updates in  $O(\log n + \delta)$  amortized time. Our dynamic dictionary supports range queries in  $O(\log n + \delta + k)$  worst case time, where k is the size of the output.

### 1.5 Outline

The remainder of the dissertation is structured as follows. We give a thorough discussion about hardware in Chapter 2, and we discuss the various computation models, including related work, in Chapter 3. Chapters 4-10 contain the technical contributions of this dissertation. In Chapter 4 we discuss cache-aware and cache-oblivious adaptive sorting. Chapter 5 is devoted to showing that the running time of Quicksort is adaptive with respect to the number of inversions in the input, and we show adaptive behaviors also for Mergesort and Heapsort. We prove lower and upper bounds stating optimal tradeoffs between branch mispredictions and comparisons for sorting and adaptive sorting algorithms in Chapter 6, and then we discuss the skewed binary search trees in Chapter 7. In Chapter 8 we focus on streaming algorithms, and show how to achieve efficient algorithms for several fundamental combinatorial problems by simulating parallel algorithms. Finally, we introduce resilient priority queues in Chapter 9 and optimal resilient dictionaries in Chapter 10.

## Chapter 2

## Hardware

Hardware /nm./: the part of the computer that you can kick. — Unknown

In this chapter we give a thorough description of the architecture of nowadays computers, emphasizing the key components affecting the running time. We first describe the CPU in Section 2.1, and then the memory hierarchy in Section 2.2. Finally, in Section 2.3 we discuss memory corruptions.

### 2.1 Processor

The processor is the core of any computing system. Nowadays processors are highly complex electronic machineries, and processor technologies evolve at amazing rates. For instance, due to fast progress in nanotechnology, in 1997 the Intel MMX processor was designed on 350nm (nano-meters) technology, nowadays processors use 65nm technology, and the predictions state that in about 2010 processor technology will be done on 32nm [97, 98]. This huge progress allows a typical nowadays processor to contain as many as 125 million transistors on a die size of only  $112 \text{mm}^2$  [17].

We introduce in Figures 2.1 and 2.2 the architectures of two popular processors, the Pentium 4 and AMD Opteron respectively, as illustrated in [17] and [73]. The two architectures are very similar and the key components are the same. They both contain a L1 data cache and L1 instruction cache, the latter denoted Execution Trace Cache for the Intel architecture, as well as an unified L2 cache. Both architectures handle integer operations separately from floating point and multimedia operations. The main difference between them is that the instruction cache for the Pentium architecture contains decoded instructions unlike the AMD. Due to the more extensive documentation at our disposal, in the remainder of this section we restrict ourselves to give more detail for the Pentium 4.

The typical execution flow for the Intel Pentium 4 architecture starts with prefetching, decoding and storing the resulted micro-operations ( $\mu$ ops) in the Execution Trace Cache. The  $\mu$ ops are then scheduled for execution in one of the integer Arithmetic and Logical Units (ALU) or one of the two blocks dedicated

Figure 2.1: The architectures for Intel Pentium 4 [17].

Figure 2.2: The architectures for AMD Opteron [73].

to floating point (FP) instructions. The instructions are executed once the operands are fetched from the data cache.

To improve the instruction execution of the CPU, a series of enhancements and optimizations have been performed. For instance, in the case of conditional branches, a branch predictor has been added to predict the output of a given branch prior to its execution, such that the instructions that follow the branch can be prefetched. A thorough description of branch predictors is given in Section 2.1.2. Another enhancement concerns store-to-load forwarding and concerns scheduling the instructions to the various execution units. When an instruction is scheduled for execution, its data may be the result of another instruction not yet executed, and the processor needs to make sure the given instruction has this data. For this purpose, the Pentium 4 processor employs a Store Forwarding Buffer which contains the results of previous instructions, or previous stores for the L1 data cache.

A recent and very significant improvement in processor design concerns developing multi-core processors. A multi-core processor contains several execution cores, and the main motivation for using them lies in the relationship between frequency and power. For instance, by overclocking a processor to achieve a 13% gain in performance, the price to pay is an increase by 73% in power consumed, while by losing 13% in frequency by underclocking the processor, the power consumption reduces to about a half. Therefore, using two under-clocked cores in a multi-core processor, one can achieve 73% more in performance for the power used by a regular single-core processor [98], or for the same performance significant gains are achieved in power consumption.

In the following we analyze the components that are the main time consumers for the processors in practice and which are discussed in the remainder of the dissertation. We first describe the execution core, and then we focus on branch mispredictions. The L1 and L2 caches as well as the TLB (Translation Lookaside Buffer), though parts of the processor, will be discussed in Section 2.2, which is devoted to the study of the memory hierarchy.

#### 2.1.1 Execution engine

Processor performance often refers to the amount of time it takes to execute some given application, or the ability to run multiple applications in a given period of time. Usually it is quantified by multiplying the frequency and the IPC (Instructions Per Cycle) [118], hence in this acception the performance of a processor is given by the speed at which the processor executes instructions. For a long time processor design engineers worked mostly on increasing the frequency, which reached 3 Ghz in 2002 from only 5 Mhz in 1983. By 2002, due to limitations generated by power densities and the resulting heat, increasing the IPC receives more and more attention. Two direction have been adopted to increase the IPC. The first one consists in extending the number of instructions as well as increasing the instruction set performed by a processor in a cycle, and the second one concerns developing multi-core processors [98].

Taking a closer look at the architecture of the Pentium 4, see e.g. Figure 2.1, we notice that there are three execution blocks dedicated to integer instructions and two for floating point instructions. Furthermore, two of the integer execution blocks operate at double speed and can execute two instructions in a cycle.

#### 2.1.2 Branch mispredictions

Nowadays CPUs have high memory bandwidth and increased pipelines, e.g. Intel Pentium 4 Prescott has a 31 stage pipeline. The high memory bandwidth severely lowers the effect of caching over the actual running time when computation takes place in the internal memory. More precisely, faster memory

Figure 2.3: A classification of the branch prediction schemes. The most popular branch predictors in each category are emphasized.

transfers imply that the overhead incurred by a cache miss is less costly and thus has a smaller effect on the running time of an algorithm.

When a conditional branch enters the execution pipeline of the CPU, its outcome is not known and therefore must be predicted. If the prediction is incorrect, the pipeline is flushed as it contains instructions corresponding to a wrong execution path. Obviously, each branch misprediction results in performance losses, which increase with the length of the pipeline.

Several branch prediction schemes have been proposed. A classification of the branch prediction schemes is given in Figure 2.3.

In a static prediction scheme, every branch is predicted in the same direction every time according to some simple heuristics, e.g. all forward branches taken, all backward branches not taken. Although simple to implement, their accuracy is low and therefore they are not widely used in practice.

The dynamic schemes use the execution history when predicting a given branch. In the local branch prediction scheme (see Figure 2.4, left) the direction of a branch is predicted using its past outputs. It uses a *pattern history table* (*PHT*) to store the last branch outcomes, indexed after the lower n bytes of the address of the branch instruction. However, the direction of a branch might depend on the output of other previous branch instructions and the local prediction schemes do not take advantage of it. To deal with this issue global branch prediction schemes were introduced [122]. They use a *branch history register* (BHR) that stores the outcome of the most recent branches. The different global prediction schemes vary only in the way the prediction table is looked up.

Three global branch prediction schemes proved very effective and are widely implemented in practice [83]. The GAg (Figure 2.4, middle) uses only the last m bits of the BHR to index the pattern history table, while *gshare* address the PHT by xor-ing the last bits n of the branch address with the last m bits of the BHR. Finally *gselect* concatenates the BHR with the lower bits of the branch address to obtain the index for the PHT.

The predictions corresponding to the entries in the PHT are usually obtained by the means of *two-bit saturating counters*. A two-bit saturating counter is an automaton consisting of four states, as shown in Figure 2.5.

#### 2.1. Processor

Figure 2.4: Branch prediction schemes.

Figure 2.5: Two-bit saturating counter.

Note that for the dynamic branch prediction schemes the same index in the *PHT* might correspond to several branches which would affect each other's predictions, constructively or destructively. This is known as the *aliasing effect* and reducing its negative effects is one of the main research areas in branch prediction schemes design.

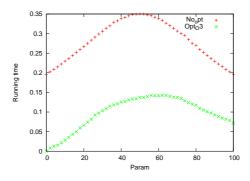

We show the effect of branch mispredictions over the running time by the means of a simple example. We generate a random array a of fixed length  $n = 2 \times 10^7$ , with a[i] chosen uniformly at random in  $[1 \dots 100]$ . In a left-to-right scan we count the number of elements greater and smaller or equal than a given parameter *param*, see e.g. the C source code in Figure 2.6. We measure the running time of this code in two different settings, optimized with optimization -O3 and using no optimizations respectively, for different values of parameter param in the range  $[0, \ldots, 101]$ . Intuitively, the inner branch is easy to predict when the value of *param* is close to the endings of the interval, and becomes very hard to predict when the value of *param* gets closer to the middle of interval. In Figure 2.7 we present the results of our experiments, where each plotted value represents the average over three different runs. When using no optimizations, the chart has a symmetric behavior, the maximum running time is achieved for  $param \approx 50$ , and the maximum running time is larger by about 75% than the minimum running time. When using optimization -O3, the running times are significantly faster, and the maximum running time is about 400% larger than the minimum running time. However, the chart does not exhibit a symmetric behavior, but the maximum running time is achieved fir param  $\approx 65$ , and the difference in running times for  $param \approx 0$  and  $param \approx 100$  is of about 300%. By the means of a brief inspection of the assembly code, we explain the different behaviors by the fact that in the optimized code when the branch is taken, corresponding to a value larger than *param*, the code contains a jump instruction more than in the case when the branch is not taken, and this does not happen in the case when the code is not optimized.

```

for(i=0;i<n;i++)

if(a[i]>param)

g++;

else

s++;

```

Figure 2.6: Simple example demonstrating the effect that branch mispredictions have over the running time. The size of the array a is  $n = 2 \times 10^7$  and the values a[i] are generated uniformly at random in  $[1, \ldots, 100]$ .

Sanders and Winkel [103] gave a distribution based sorting algorithm and show that in certain cases branch mispredictions can be avoided by using predicated instructions available in certain processors, e.g. Intel Itanium. A predicated instruction is an instruction which is associated a predicate. The instruction is executed if the predicate is true, and is discarded otherwise.

### 2.2 Memory hierarchy

This section is devoted to the study of the memory hierarchy found in modern computers. Nowadays computers contain several memory levels, each level having smaller size and access time than the next one. Typically, a desktop computer contains CPU registers, L1, L2, and L3 caches, main memory and hard-disk. From the CPU to the hard-disk, each level has a smaller size and access time compared to the next level, see e.g. Figure 2.10. The access time increases from one or even half a cycle for registers to around 1,000,000 cycles for the disk [61]. To amortize the cost of a memory access per element, data is

Figure 2.7: The running time of the code in Figure 2.6, using optimization -O3 and no optimization at all, for different values of parameter *param*.

transferred in blocks between consecutive memory levels. Upon a data request for a given level, if the data requested is contained in that level we say we have a *cache hit*, and we say a *cache miss* or *cache fault* occurred otherwise. When a cache fault occurs, the data required is fetched from the next level at the cost of a block transfer, and a block is evicted from the current level. To decide which block to be evicted, several replacement strategies were proposed, out of which LRU (Least Recently Used) and its variants became very popular.

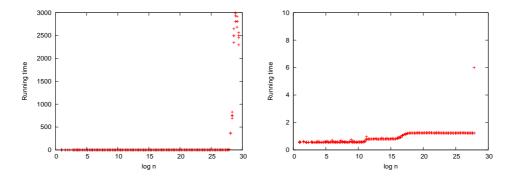

Similarly to branch mispredictions, we demonstrate the effect that memory transfers have over the running time using a simple example. We consider an array of size n, where n is a parameter, and access its elements in a cyclic manner for a constant number of steps r, see. e.g. the source code in Figure 2.8. We compiled our code using optimization level -O3, and to avoid compiler optimizations disregarding the memory accesses we compute the sum of the elements visited and return it.

```

r=80000000;s=0;

for(i=0;i<n-1;i++)

a[i]=i+1;

a[n-1]=0;

/* start timing */

for(i=0;i<r;i++)

{

s+=a[k];

k=a[k];

}

/* end timing */

return s;

```

Figure 2.8: Simple example demonstrating the effect that memory transfers have over the running time. We consider an array of size n and perform  $r = 8 \times 10^8$  element accesses in a cyclic manner, by computing the sum. We measure the running time of the code indicated by comments.

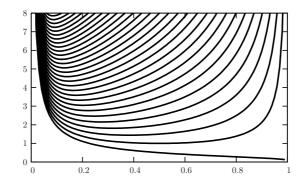

We are interested in the running time of the code indicated by the appropriate comments, when varying the size n of the array. In Figure 2.9 we show the experimental results. First, we note that for  $\log n \approx 28$  the running time increases by a factor of about 2000 (Figure 2.9, left). This step corresponds to the limit when the array still fits in the internal memory. Intuitively, as long as the arrays fits in the internal memory the memory accesses take little time and the computation is very fast. When the array does not fit in the internal memory, initially the first part of array fills completely the main memory. After this moment, given the fact that the replacement policy usually removes the least recently accessed block, each block access results in a cache miss and, given the large access times for disks, the running time increases dramatically. However, in Figure 2.9 (right), by restricting the range of the y-axis, we show that a similar behavior is observed between the other levels of the memory hierarchy, resulting in running time increases for  $\log n \approx 12$  and  $\log n \approx 17$ , corresponding to thresholds when the array does not fit in the L1 and the L2 cache respectively.

Figure 2.9: Running time of the highlighted code in Figure 2.8. The right chart plots the same data as the left chart, but restricts the range of the y-axis.

Given their effect over the running time, it becomes obvious that minimizing memory transfers, especially between disk and the main memory, is a key factor in achieving fast algorithms in practice. We describe the structure of the different memory levels and give more insights for their behavior in practice. We start by describing the registers and caches, then we move on to introduce the main memory, and we conclude by presenting the hard-disk.

#### 2.2.1 Registers and caches

The registers are memory cells with very fast access times built inside the main core of the processor. The data is loaded into the registers from the cache memory before being processed and is stored still in the registers after processing. Since there is a big gap between the speeds at which the processor and the RAM memory operate, modern computers employ a few intermediate memories, called cache memories, which have small sizes, but fast access times.

We briefly introduce the organization of cache memories. As with all levels in the memory hierarchy, a cache memory is a collection of disjointed blocks of constant size. We first describe the direct mapped and fully-associative caches. The direct mapped cache are easy to implement in practice, but achieve rather

Figure 2.10: Typical memory hierarchy in a modern computer.

poor performances, while fully associative caches yield good performances at high design cost. We then introduce the set associative caches, which are a compromise between direct-mapped caches and fully-associative caches and which are widely implemented in practice.

A cache is denoted *direct mapped* when the location of each block in the cache is given by its memory address. In this case the replacement policy becomes trivial, since the page to be evicted is given by the memory address of the incoming cache line. Given the trivial replacement policy, direct-mapped caches are easy to implement in practice. However, because the replacement policy is decided by the memory address and not by the usage, the use of direct-mapped caches can cause significant performance losses by *thrashing*, when useful information is evicted from the cache. For instance, repeated interleaved accesses of two memory blocks mapping to the same cache location results in a cache miss for each access.

A *fully-associative* cache dramatically improves the performance of directmapped caches by using a much more sophisticated replacement strategy. Deciding which page to be evicted considers the usage of the different blocks instead of their memory addresses. A typical strategy is LRU (Least Recently Used), which replaces the oldest block with respect to the time of the last usage. Unfortunately, the very good performance achieved by fully-associative caches in practice involves non-negligible costs in circuitry required to keep track of the usage of all the blocks in the cache.

To combine the performance of the fully-associative caches and the simple design of the direct-mapped ones, hardware designers introduced *n*-way set associative caches. A *n*-way set associative cache is a collection of *n* direct-mapped caches, referred to as sets [115]. The replacement strategy decides the block to be evicted by first choosing one of the sets according to LRU or any other replacement strategy, and then decides the block to be evicted in the chosen set according to the memory address of the incoming block. This way, the circuit complexity is maintained simple enough, and thrashing is reduced. For a more comprehensive discussion on cache memories, we refer the interested reader to [63, 111].

We now describe the cache memories in a typical computer.

- CPU caches. Modern computers include at least two levels of cache memories in their architecture. Usually processors include in their architecture two L1 cache memories, namely the instruction cache and the data cache, to store instructions to be executed and the data required by the programs respectively. Because the two L1 caches work independently, we achieve a significant increase in performance. On the other hand, it is common that there is only one L2 and (if available) L3 cache, which is unified, meaning that it contains both instructions and data. For better performance, a typical design has the L1 caches on the CPU chip, the L2 cache inside the CPU package, and the L3 cache (if available) on the motherboard.

- TLB. The Translation Lookaside Buffer (TLB) is a small fully-associative cache memory used to store associations between virtual memory addresses and physical memory addresses. Since translating a virtual memory address

into a physical memory address is a rather costly operation, storing this information in a cache inside the CPU is necessary to avoid severe performance losses. Some processors, such as UltraSPARC, go even further and include two TLBs in their designs, to store associations between virtual and physical memory addresses for instructions and data separately [115].

#### 2.2.2 Main memory

Typically, the main memory of a computer is a RAM (Random Access Memory), has much larger size than the cache memories and is dedicated to store vast amounts of information required by the various applications. The time required for accessing a block in a RAM is approximately the same for all blocks and is reasonably small.

#### 2.2.3 Hard-disk

Unlike RAM memories which consist of integrated circuits, the hard-disk is a highly mechanical component. It consists of several platters, and each face of a platter is assigned a read/write head. The surface of each face of a platter is divided into a number of concentric circles denoted tracks, and each track is further subdivided in a number of sectors. The data is written to and read from the sectors. We note that since the inner tracks have a much shorter length than the outer tracks, the number of sectors in a track is not constant. To access the data on a platter, the head first identifies the track to access and then the platter is rotated until the required location is encountered. We note that the read/write head can move only inwards and outwards and can not be placed always at the exact location to access, but merely on the right track and most of the times rotating the platter is required.

The major advantage of hard-disks over RAM memories is that they are nonvolatile and thus the information stored is persistent upon power interruptions. However, the non-volatility comes at the price of very slow access times. For example, typical access times are a few tens of nanoseconds for main memories and at least ten milliseconds for hard-disks [111]. As a final remark, the time spent on positioning the head on the correct track is much larger than the time needed to rotate the platter and therefore accessing the data sequentially is much faster than performing random accesses.

### 2.3 Memory corruptions

Memory devices continually become smaller, work at higher frequencies and lower voltages, and in general have increased circuit complexity [32]. Unfortunately, these improvements come at the cost of reliability [113,114]. A number of factors, such as alpha particles, infrared radiation, and cosmic rays, can cause *soft memory errors*, sometimes referred as *single-event upsets*, where a bit flips and as a consequence the value stored in the corresponding memory cell is corrupted. An unreliable memory can cause problems in most software ranging from the harmless to the very serious, such as breaking cryptographic protocols [18, 120], taking control of a Java Virtual Machine [57] or breaking smart-cards and other security processors [5, 6, 108]. Furthermore, many modern computing centers consist of relatively cheap of-the-shelf components, and the large number of individual memories involved in these clusters substantially increase the frequency of memory corruptions in the system. Hence it is crucial that the software running on these machines is robust. Since the amount of cosmic rays increases dramatically with altitude, soft memory errors are of special concern in fields like avionics or space research. Furthermore, soft memory error rates are expected to rise for both DRAM and SRAM memories [113].

At the hardware level, the soft memory errors can be handled by means of error detection mechanisms such as redundancy or error correcting codes. Unfortunately, implementing these mechanisms incur penalties with respect to performance, size and money, and therefore memories using these technologies are rarely found in large scale computing clusters or ordinary workstations. Recent solutions to cope with soft-memory errors in cache memories include replicating some "hot" blocks, i.e. blocks that are accessed often, in cache memories or even an extra fully-associative L1 cache devoted to storing these hot blocks [123, 124].

On the software level, a series of low-level techniques have been proposed for dealing with the soft memory errors, many of them coping with corrupted instructions. Examples include algorithm based fault tolerance [67], assertions [101], control flow checking [121], or procedure duplication [96].

For more details concerning soft memory errors we refer the interested reader to comprehensive surveys [102, 109].

As a final remark, high energy particles originating from alpha particles can cause errors not only in memory locations but also in combinational logic in the processor. In this case the shrinking geometries and increased pipeline depths play a major role in increasing the frequency of combinational logic errors, and studies estimate that between 1992 and 2011 the frequency of these errors will increase nine orders of magnitude up to a level comparing to that of soft memory errors in memories not implementing any error protection [107].

# Chapter 3

## Modeling Hardware

Make everything as simple as possible, but not simpler. — Albert Einstein

When counting the occurrences of the different hardware factors (e.g. CPU instructions, branch mispredictions, I/O transfers etc.) during the lifetime of an algorithm, models are employed to provide frameworks in which algorithms are easy to design and analyze. Basically, a model can be seen as a simplification of the targeted hardware by taking into account only the relevant features. Models are required to be simple enough to make algorithm design and analysis as simple as possible, but in the same time they need to be accurate in capturing the hardware they model.

In this chapter we introduce several models used for modeling the different hardware factors affecting the running time of the algorithms, as well as relevant related work for each of them. In Section 3.1 we introduce two popular models used for decades in algorithm design, the *RAM model* and the *comparison model*. In Section 3.2 we describe various approaches employed to achieve branch mispredictions complexities for searching and sorting. We introduce two models handling memory transfers, the I/O model and the *cache oblivious model* in Section 3.3, while in Section 3.4 we present several models used to design and analyze streaming algorithms. This chapter concludes with Section 3.5, which is devoted to models related to memory corruptions and computation with unreliable information.

## 3.1 Traditional models